öĄūųļŖ┬ĘĘų×ķĮM║Ž▀ē▌ŗļŖ┬Ę║═Ģrą“▀ē▌ŗļŖ┬Ęā╔ŅÉŻ¼ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─╠ž³c╩Ū▌ö│÷ą┼╠¢ų╗╩ŪįōĢrĄ─▌ö╚ļą┼╠¢Ą─║»öĄŻ¼┼cäeĢr┐╠Ą─▌ö╚ļĀŅæB¤oĻPŻ¼╦³╩Ū¤oėøæø╣”─▄Ą─ĪŻ▀@ę╗š┬╬ęéāüĒīW┴ĢĮM║Ž▀ē▌ŗļŖ┬ĘĪŻ▀@ę╗š┬╩Ū▒Ššn│╠Ą─ųž³cā╚╚▌ų«ę╗

╬ęéāį┌īW┴ĢĢr░č▀@ę╗š┬Ą─ā╚╚▌Ęų×ķŻ║

Īņ4Īó1 ▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷

Īņ4Īó2 ▀ē▌ŗļŖ┬ĘĄ─įOėŗ

Īņ4Īó3 │Żė├Ą─ĮM║Ž▀ē▌ŗ

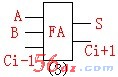

Īņ4Īó1 ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷

ę╗Ż║ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷ Ż©1Ż®Ż║ėąĮoČ©Ą─▀ē▌ŗļŖ┬ĘłDŻ¼īæ│÷▌ö│÷Č╦Ą─▀ē▌ŗ▒Ē▀_╩ĮŻ╗ Ż©2Ż®Ż║┴ą│÷šµųĄ▒ĒŻ╗ Ż©3Ż®Ż║═©▀^šµųĄ▒ĒĖ┼└©│÷▀ē▌ŗ╣”─▄Ż¼┐┤įŁļŖ┬Ę╩Ū▓╗╩ŪūŅ└ĒŽļŻ¼╚¶▓╗╩ŪŻ¼ätī”Ųõ▀MąąĖ─▀MŻ╗

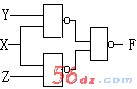

╬ęéāī”ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─Ęų╬÷ĘųęįŽ┬ÄūéĆ▓Į¾EŻ║

ĪŻ Ą┌ę╗▓ĮŻ║īæ▀ē▌ŗ▒Ē▀_╩ĮĪŻ╬ęéāė╔Ū░╝ēĄĮ║¾╝ēīæ│÷Ė„ķT▀ē▌ŗ▒Ē▀_╩Į

└²1Ż║ęčų¬ėę├µĄ─▀ē▌ŗļŖ┬ĘłDŻ¼įćĘų╬÷Ųõ╣”─▄ĪŻ

P=A+B S=A+P=AB W=B+P=AB

F=S+W=AB+A B

Ą┌Č■▓ĮŻ║┴ąšµųĄ▒ĒŻ©╚ńėęłD╦∙╩ŠŻ®ĪŻ

Ą┌╚²▓ĮŻ║▀ē▌ŗ╣”─▄├Ķ╩÷▓óĖ─▀MįOėŗĪŻ

Å─šµųĄ▒Ēųą┐╔ęį┐┤│÷▀@╩Ūę╗éĆČ■ūā┴┐Ī░═¼╗“Ī▒ļŖ┬ĘĪŻįŁļŖ┬ĘįOėŗ▓╗║Ž└ĒŻ¼╦³ų╗ąĶę╗éĆ"═¼╗“"ķT╝┤┐╔.

Īņ4Īó2 ĮM║Ž▀ē▌ŗļŖ┬ĘĄ─įOėŗ

ę╗Ż║ĮM║ŽļŖ┬Ę▀ē▌ŗļŖ┬ĘĄ─įOėŗ

ļŖ┬ĘįOėŗĄ─╚╬䚊═╩ŪĖ∙ō■╣”─▄įOėŗļŖ┬ĘŻ¼ę╗░Ń░┤╚ńŽ┬Ą─▓Į¾E▀MąąŻ║

Ż©1Ż®░č▀ē▌ŗ├³Ņ}ōQ×ķšµųĄ▒ĒŻ╗▀@ę╗▓Į╬ęéāę¬Å─ęįŽ┬ÄūéĆĘ┤├µ┐╝æ]

ė├ėó╬─ūų─Ė┤·▒Ē▌ö╚ļ╗“▌ö│÷Ż╗

ĘųŪÕÄūéĆ▌ö╚ļĪó▌ö│÷Ż╗

ĘųŪÕ▌ö╚ļ║═▌ö│÷ų«ķgĄ─ī”æ¬ĻPŽĄĪŻ

Ż©2Ż®░č▀ē▌ŗ║»öĄ▀Mąą╗»║åŻ¼╗»║åĄ─ą╬╩Įät╩ŪĖ∙ō■╦∙▀xė├Ą─▀ē▌ŗķTüĒøQČ©Ż╗

Ż©3Ż®Ė∙ō■╗»║åĮY╣¹║═╦∙▀xČ©Ą─ķTļŖ┬ĘŻ¼«ŗ│÷▀ē▌ŗļŖ┬ĘłDĪŻ

└²Ż║ įOėŗ╚²ūā┴┐▒ĒøQŲ„Ż¼ŲõųąXŠ▀ėąĘ±øQÖÓĪŻ

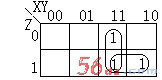

Ą┌ę╗▓ĮŻ║┴ą│÷šµųĄ▒ĒĪŻŻ©╚ńėę╔ŽłDŻ®

įOXĪóYĪóZĘųäe┤·▒Ēģó╝ė▒ĒøQĄ─ūā┴┐Ż╗F×ķ▒ĒøQĮY╣¹Ż¼

╬ęéā░čūā┴┐ęÄČ©×ķŻ║XĪóYĪóZ×ķ1▒Ē╩Š┘Ø│╔Ż╗×ķ0▒Ē╩ŠĘ┤ī”ĪŻ

F×ķ1▒Ē╩Š═©▀^Ż╗×ķ0▒Ē╩Š▒╗ʱøQĪŻ

Ą┌Č■▓ĮŻ║╗»║å▀ē▌ŗ║»öĄĪŻ

╬ęéā▀xė├┼cĘŪ▀ē▌ŗüĒīŹ¼FĪŻė├┐©ųZłDüĒ╗»║åŻ©╚ńėęųąłDŻ®F=![]()

Ą┌╚²▓ĮŻ║«ŗ▀ē▌ŗļŖ┬ĘĪŻŻ©╚ńėęłDŻ®

Īņ4Īó3 │Żė├Ą─ĮM║Ž▀ē▌ŗ

│Żė├ĮM║Ž▀ē▌ŗĄ─ĘNŅÉ║▄ČÓŻ¼ų„ę¬ėą╚½╝ėŲ„Īóūg┤aŲ„ĪóŠÄ┤aŲ„ĪóČÓ┬Ę▀xō±Ų„Ą╚Ż¼Ž┬├µ╬ęéāĘųäe░č╦³éāĮķĮBę╗Ž┬ĪŻ

ę╗Ż║░ļ╝ėŲ„║═╚½╝ėŲ„

į┌öĄūųŽĄĮyųą╦Ńąg▀\╦ŃČ╝╩Ū└¹ė├╝ėĘ©▀MąąĄ─Ż¼ę“┤╦╝ėĘ©Ų„╩ŪöĄūųŽĄĮyųąūŅ╗∙▒ŠĄ─▀\╦Ńå╬į¬ĪŻė╔ė┌Č■▀MųŲ▀\╦Ń┐╔ęįė├▀ē▌ŗ▀\╦ŃüĒ▒Ē╩ŠŻ¼ę“┤╦╬ęéā┐╔ęįė├▀ē▌ŗįOėŗĄ─ĘĮĘ©üĒįOėŗ▀\╦ŃļŖ┬ĘĪŻ╝ėĘ©į┌öĄūųŽĄĮyųąĘų×ķ╚½╝ė║═░ļ╝ėŻ©Ą┌ę╗š┬╬ęéāęčĮøĮķĮB┴╦Ż®╦∙ęį╝ėĘ©Ų„ę▓Ęų×ķ╚½╝ėŲ„║═░ļ╝ėŲ„ĪŻ

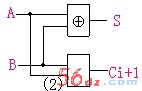

Ż©1Ż®░ļ╝ėŲ„įOėŗ

░ļ╝ėŲ„▓╗┐╝æ]Ą═╬╗Ž“▒Š╬╗Ą─▀M╬╗Ż¼ę“┤╦╦³ėąā╔éĆ▌ö╚ļČ╦║═ā╔éĆ▌ö│÷Č╦ĪŻ

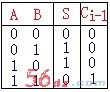

įO╝ėöĄŻ©▌ö╚ļČ╦Ż®×ķAĪóB Ż╗║═×ķS Ż╗Ž“Ė▀╬╗Ą─▀M╬╗×ķCi+1ĪŻ

╦³Ą─šµųĄ▒Ē×ķŻ║╚ńėęłD╦∙╩Š

║»öĄĄ─▀ē▌ŗ▒Ē▀_╩Į×ķŻ║ S=AB+AB Ż╗ Ci+1=AB

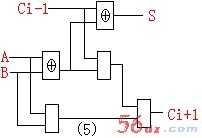

▀ē▌ŗļŖ┬ĘłDŻ©ė├«É╗“ķT║═┼cķTśŗ│╔Ż®×ķŻ║╚ńėęłD(2)╦∙╩Š

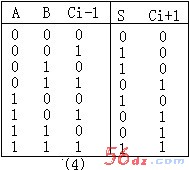

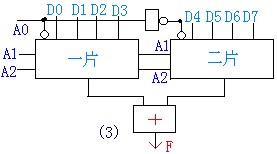

Ż©2Ż®╚½╝ėŲ„Ą─įOėŗŻ©╦³Ą─▀ē▌ŗĘ¹╠¢×ķłD(3)╦∙╩ŠŻ®

ė╔ė┌╚½╝ėŲ„┐╝æ]Ą═╬╗Ž“Ė▀╬╗Ą─▀M╬╗Ż¼╦∙ęį╦³ėą╚²éĆ▌ö╚ļČ╦║═ā╔éĆ▌ö│÷Č╦ĪŻ

įO▌ö╚ļūā┴┐×ķŻ©╝ėöĄŻ®AĪóBĪó Ci-1Ż¼▌ö│÷ūā┴┐×ķ SĪó Ci+1

╦³Ą─šµųĄ▒Ē×ķŻ║╚ńłD(4)╦∙╩Š

║»öĄĄ─▀ē▌ŗ▒Ē▀_╩Į×ķŻ║S=ABCi-1+ABCi-1+ABCi-1+ABCi-1=A![]() B

B![]() Ci-1

Ci-1

Ci+1=ABCi-1+ABCi-1+ABCi-1+ABCi-1 =Ż©A![]() BŻ®Ci-1+AB

BŻ®Ci-1+AB

▀ē▌ŗļŖ┬ĘłD(ė├«É╗“║═┼cķTśŗ│╔Ż®×ķŻ║╚ńłD(5)╦∙╩Š

Ż©3Ż®╚½╝ėŲ„Ą─æ¬ė├

ę“×ķ╝ėĘ©Ų„╩ŪöĄūųŽĄĮyųąūŅ╗∙▒ŠĄ─▀ē▌ŗŲ„╝■Ż¼╦∙ęį╦³Ą─æ¬ė├║▄ÅVĪŻ╦³┐╔ė├ė┌Č■▀MųŲĄ─£pĘ©▀\╦ŃĪó│╦Ę©▀\╦ŃŻ¼BCD┤aĄ─╝ėĪó£pĘ©Ż¼┤aĮMūāōQŻ¼öĄ┤a▒╚▌^Ą╚ĪŻ

└² 1Ż║ė├╚½╝ėŲ„śŗ│╔Č■▀MųŲ£pĘ©Ų„ĪŻ

ęį╦─╬╗Č■▀MųŲ×ķ└²ĪŻŻ©£pĘ©┐╔▐DōQ×ķ╝ėča▀\╦ŃŻ®

įOā╔ĮM╦─╬╗Č■▀MųŲĘųäe×ķX3X2X1X0║═Y3Y2Y1Y0,░čY3Y2Y1Y0Ž╚▀MąąŪ¾ča╚╗║¾į┘▀Mąą╝ėĘ©▀\╦ŃĪŻ

ę“×ķŪ¾ča╩Ūų╬╗Ū¾Ę┤║¾į┘╝ėĪ░1Ī▒╦∙ęį╦³Ą─▀ē▌ŗļŖ┬ĘłD×ķ╚ńłD(6)╦∙╩Š:

└² 2Ż║▓╔ė├╦─╬╗╚½╝ėŲ„═Ļ│╔8421BCD┤a▐DōQ×ķėÓ3┤·┤aĪŻ

ė╔ė┌8421BCD┤a╝ė0011╝┤×ķėÓ3┤·┤aŻ¼ę“┤╦▐DōQļŖ┬ĘŠ═╩Ū╝ėĘ©ļŖ┬ĘĪŻ

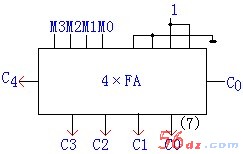

įO8421BCD┤a╦─╬╗ėųĖ▀╬╗ĄĮĄ═╬╗×ķM3ĪóM2ĪóM1ĪóM0Ż¼ėÓ3┤·┤aĄ─╦─╬╗ė╔Ė▀ĄĮĄ═×ķC3ĪóC2ĪóC1ĪóC0 ĪŻ

╦³Ą─▀ē▌ŗļŖ┬ĘłD×ķ╚ńłD(7)╦∙╩Š:

Č■Ż║ŠÄ┤aŲ„║═ūg┤aŲ„

ųĖČ©Č■▀MųŲ┤·┤a┤·▒Ē╠žČ©Ą─ą┼╠¢Ą─▀^│╠Š═ĮąŠÄ┤aĪŻ░č─│ę╗ĮMČ■▀MųŲ┤·┤aĄ─╠žČ©║¼┴xūg│÷Ą─▀^│╠Įąūg┤aĪŻ

Ż©1Ż®ŠÄ┤aŲ„ ę“×ķn╬╗Č■▀MųŲöĄ┤aėą2nĘNĀŅæBŻ¼╦∙ęį╦³┐╔┤·▒Ē2nĮMą┼ŽóĪŻ╬ęéāį┌ŠÄ┤a▀^│╠ųąę╗░Ń╩Ū▓╔ė├ŠÄ┤aŠžĻć║═ŠÄ┤a▒ĒŻ¼ŠÄ┤aŠžĻćŠ═╩Ūį┌┐©ųZłD╔ŽųĖČ©├┐ę╗ĘĮĖ±┤·▒Ē─│ę╗ūį╚╗öĄŻ¼░č▀@ą®ūį╚╗öĄ╠Ņ╚ļŽÓæ¬Ą─ĘĮĖ±ĪŻ

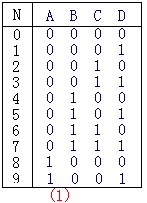

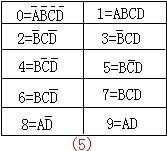

└² 1Ż║░č0Īó1Īó2Īó...Īó9ŠÄ×ķ5421BCD┤a.

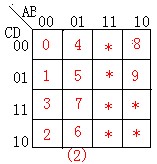

Ž╚üĒ┤_Č©ŠÄ┤a▒Ē╚ńłD(1)╦∙╩Š║═ŠÄ┤aŠžĻć╚ńłD(2)╦∙╩Š:

ė╔ŠÄ┤a▒Ē┤_Č©Ė„▌ö│÷Č╦Ą─▀ē▌ŗ▒Ē▀_╩Į╩ŪŻ║

A=5+6+7+8+9

B=4+9

C=2+3+7+8

D=1+3+6+8

Ė∙ō■▀@ą®▒Ē▀_╩Į┐╔ė├╗“ķTĮM│╔

▀ē▌ŗļŖ┬Ę╚ńłD(3)╦∙╩Š:

Ż©2Ż®Ż║ūg┤aŲ„ ŠÄ┤aĄ──µ▀^│╠Š═╩Ūūg┤aĪŻ

ūg┤aŠ═╩Ū░č┤·┤aūg×ķę╗Č©Ą─▌ö│÷ą┼╠¢Ż¼ęį▒Ē╩Š╦³Ą─įŁęŌĪŻīŹ¼Fūg┤aĄ─ļŖ┬ĘŠ═╩Ūūg┤aŲ„ĪŻ

ūg┤aŲ„┐╔Ęų×ķČ■▀MųŲūg┤aŲ„Īó╩«▀MųŲūg┤aŲ„Īó╝»│╔ūg┤aŲ„║═öĄūų’@╩Šūg┤a“īäėļŖ┬ĘĪŻŲõųąČ■▀MųŲūg┤aŲ„╩Ūę╗ĘNūŅ║åå╬Ą─ūā┴┐ūg┤aŲ„,╦³Ą─▌ö│÷Č╦╚½╩ŪūŅąĪĒŚĪŻ

└² 2Ż║įOėŗę╗ūg┤aļŖ┬Ę░č8421BCD┤aĄ─0Īó1Īó2Īó...Īó9ūg│÷üĒ.

╦─╬╗Č■▀MųŲėą╩«┴∙ĘNĀŅæBŻ¼Č°īŹļHų╗ąĶę¬╩«ĘNŻ¼ę“┤╦ŲõėÓĒŚū„¤oĻPĒŚ┐╝æ].

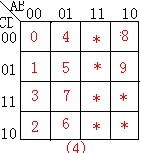

ŲõŠÄ┤aŠžĻć×ķ╚ńłD(4)╦∙╩Š.

╬ęéā═©▀^ŠÄ┤aŠžĻć┐╔Ą├╚ńŽ┬ūg┤aĻPŽĄŻ║╚ńłD(5)╦∙╩Š.

╦∙ęį╦³Ą─▀ē▌ŗļŖ┬ĘłD×ķŻ©ė├┼cķT║═┼cĘŪķTīŹ¼FŻ®

╚ńłD(6)╦∙╩Š:

╝»│╔ūg┤aŲ„Ą─╣żū„įŁ└Ē┼cŲõ╦³ūg┤aŲ„ę╗śėŻ¼Ą½╦³ėą╦³Ą─╠ž³c.

╦³Ą─╠ž³c×ķŻ║

▌ö╚ļ▓╔ė├ŠÅø_╝ē;(£p▌pą┼╠¢žō▌d)

▌ö│÷×ķĘ┤┤a;Ą═ļŖŲĮėąą¦(£p▌p▌ö│÷╣”┬╩)

į÷╝ė┴╦╩╣─▄Č╦.(▒Ńė┌öUš╣╣”─▄)

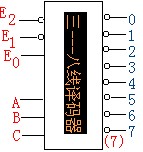

─┐Ū░│Żė├Ą─Ąõą═Ą─╝»│╔ūg┤aŲ„╩Ū╚²------░╦ūg┤aŲ„ĪŻ

╦³Ą─▀ē▌ŗĘ¹╠¢×ķ.╚ńłD(7)╦∙╩Š: ūóŻ║ŲõųąE0E1E2×ķ╩╣─▄Č╦Ż¼ų╗ėą«öE1ĪóE2×ķ0ĢrE0×ķ1Ģr┤╦ūg┤aŲ„▓┼╣żū„ĪŻ

╚²Ż║öĄō■▀xō±Ų„║═ČÓ┬ĘĘų┼õŲ„

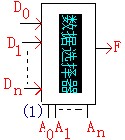

Ż©1Ż®öĄō■▀xō±Ų„ ╦³Š═╩ŪÅ─ČÓéĆ▌ö╚ļČ╦ųą▀xō±ę╗┬Ę▌ö│÷Ż¼╦³ŽÓ«öė┌ę╗éĆČÓ┬Ęķ_ĻP╦³Ą─▀ē▌ŗĘ¹╠¢╚ńłD(1)╦∙╩Š:ŲõųąD0D1ĪóĪóĪóDn╩ŪöĄō■▌ö╚ļČ╦;A0A1ĪóĪóĪóAn×ķĄžųĘūā┴┐Ż©ėąnéĆĄžųĘūā┴┐Š═ėą2néĆ▌ö╚ļČ╦Ż®.

Ż©1Ż®öĄō■▀xō±Ų„ ╦³Š═╩ŪÅ─ČÓéĆ▌ö╚ļČ╦ųą▀xō±ę╗┬Ę▌ö│÷Ż¼╦³ŽÓ«öė┌ę╗éĆČÓ┬Ęķ_ĻP╦³Ą─▀ē▌ŗĘ¹╠¢╚ńłD(1)╦∙╩Š:ŲõųąD0D1ĪóĪóĪóDn╩ŪöĄō■▌ö╚ļČ╦;A0A1ĪóĪóĪóAn×ķĄžųĘūā┴┐Ż©ėąnéĆĄžųĘūā┴┐Š═ėą2néĆ▌ö╚ļČ╦Ż®.

│Żė├Ą─ėąČ■▀xę╗Ż¼╦─▀xę╗Ż¼░╦▀xę╗║═╩«┴∙▀xę╗Ż¼╚¶ąĶĖ³ČÓätė╔╔Ž╩÷öUš╣ĪŻ

└² 3Ż║╚ńłD(2)╦∙╩ŠĄ─╦─▀xę╗öĄō■▀xō±Ų„Ż¼įćīæ│÷╦³Ą─▌ö│÷▀ē▌ŗ▒Ē▀_╩Į║═╣”─▄▒Ē

╦³Ą─▀ē▌ŗ▌ö│÷▒Ē▀_╩Į×ķ F=Ż©A0A1D0+A0A1D1+A0A1D2+A0A1D3Ż®E

╦³Ą─╣”─▄▒Ē×ķŻ║╚ńŽ┬▒Ē╦∙╩Š

Å─▒Ē╔Ž╬ęéā┐╔ęį┐┤│÷«ö╩╣─▄Č╦E×ķĪ░1Ī▒Ģr▌ö│÷×ķĪ░0Ī▒╝┤Į¹ų╣Ż¼ų╗ėą«ö╩╣─▄Č╦×ķĪ░0Ī▒Ģr▀xō±Ų„▓┼ėąą¦ĪŻ

└² 4Ż║░č╦─▀xę╗öUš╣×ķ░╦▀xę╗ĪŻ

ĄžųĘ

╩╣─▄Č╦

▌ö╚ļ

▌ö│÷

A0

A1

E

D

F

* *

1

*

0

0 0

0

D0---D3

D0

0 1

0

D0---D3

D1

1 0

0

D0---D3

D2

1 1

0

D0---D3

D3

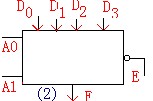

░╦▀xę╗ę¬ėą░╦éĆ▌ö╚ļūā┴┐Ż¼ę“┤╦ąĶę¬╚²éĆĄžųĘūā┴┐(╬ęéā░čŲõųąę╗éĆA0ū„×ķ╩╣─▄Č╬)Ż╗

╦─▀xę╗ų╗─▄ėą╦─éĆ▌ö╚ļūā┴┐Ż¼╦∙ęį╬ęéāąĶę¬ā╔éĆ╦─▀xę╗║═ę╗éĆĘŪķT.ĘŪķTĄ─ū„ė├╩ŪĖ─ūā╩╣─▄Č╦Ą─ļŖŲĮŻ¼£p╔┘╩╣─▄Č╦.Ž╚┴ą│÷╦³Ą─╣”─▄▒Ē╚ńŽ┬▒Ē╦∙╩Š:

▀ē▌ŗļŖ┬ĘłD╚ńłD(3)╦∙╩Š:

Ż©2Ż®ČÓ┬ĘĘų┼õŲ„ ╦³Ą─╣”─▄╩Ū░č▌ö╚ļöĄō■Ęų┼õĮo▓╗═¼Ą─═©Ą└╔ŽŻ¼ŽÓ«öė┌ę╗éĆå╬ĄČČÓöSķ_ĻPĪŻ

A0

A1

A2

D

F

0 0 0

D0----D7

D0

0 0 1

D0----D7

D1

0 1 0

D0----D7

D2

0 1 1

D0----D7

D3

1 0 0

D0----D7

D4

1 0 1

D0----D7

D5

1 1 0

D0----D7

D6

1 1 1

D0----D7

D7

ĘĄ╗žĒö▓┐

ĘĄ╗žĒö▓┐ ╦óą┬Ēō├µ

╦óą┬Ēō├µ Ž┬ĄĮĒōĄū

Ž┬ĄĮĒōĄū