什么是時(shí)序邏輯電路

在數(shù)字電路中,凡是任一時(shí)刻的穩(wěn)定輸出不僅決定于該時(shí)刻的輸入,而且還和電路原來狀態(tài)有關(guān)者都叫時(shí)序邏輯電路。時(shí)序邏輯電路結(jié)構(gòu)示意圖如圖2-41所示。時(shí)序邏輯電路的狀態(tài)是靠具有存儲功能的觸發(fā)器所組成的存儲電路來記憶和表征的。

時(shí)序邏輯電路的特點(diǎn)

1、功能特點(diǎn)

電路在某采樣周期內(nèi)的穩(wěn)態(tài)輸出Y(n),不僅取決于該采樣周期內(nèi)的“即刻輸入X(n)”,而且還與電路原來的狀態(tài)Q(n)有關(guān)。(通常Q(n)記錄了以前若干周期內(nèi)的輸入情況)。

2、結(jié)構(gòu)特點(diǎn)

除含有組合電路外,時(shí)序電路必須含有存儲信息的有記憶能力的電路:觸發(fā)器、寄存器、計(jì)數(shù)器等。

時(shí)序邏輯電路的功能

1、邏輯方程組

1)特性方程:描述觸發(fā)器邏輯功能的邏輯表達(dá)式。

2)驅(qū)動(dòng)方程:(激勵(lì)方程)觸發(fā)器輸入信號的邏輯表達(dá)式。

3)時(shí)鐘方程:控制時(shí)鐘CLK的邏輯表達(dá)式。

4)狀態(tài)方程:(次態(tài)方程)次態(tài)輸出的邏輯表達(dá)式。

5)輸出方程:輸出變量的邏輯表達(dá)式。

2、狀態(tài)表

反映輸出Z、次態(tài)Q*與輸入X、現(xiàn)態(tài)Q之間關(guān)系的表格。

3、狀態(tài)圖

反映時(shí)序電路狀態(tài)轉(zhuǎn)換規(guī)律及相應(yīng)輸入、輸出取值關(guān)系的圖形。

4、 時(shí)序圖

又叫工作波形圖,它用波形的形式形象地表達(dá)了輸入信號、輸出信號、電路的狀態(tài)等的取值在時(shí)間上的對應(yīng)關(guān)系。

時(shí)序邏輯電路的狀態(tài)轉(zhuǎn)換表、狀態(tài)轉(zhuǎn)換圖和時(shí)序圖詳解

狀態(tài)轉(zhuǎn)換表、狀態(tài)轉(zhuǎn)換圖和時(shí)序圖是時(shí)序電路特有的描述方法,描述出電路在 CP 作 用下,狀態(tài)轉(zhuǎn)換全部 過程。

一、狀態(tài)轉(zhuǎn)換表

將輸入及初態(tài)代入狀態(tài)方程和輸出方程,算出電路次態(tài)和現(xiàn)態(tài)下的輸 出值。

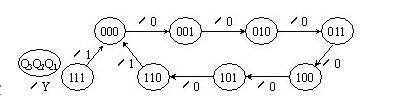

即:每 7 個(gè) CP ,電路狀態(tài)回到初態(tài)(循環(huán)變化)。可對時(shí)鐘脈沖計(jì)數(shù):每經(jīng)過 7 個(gè)時(shí)鐘脈沖, Y 輸出一個(gè)脈沖(即由 0 變 1 ,再由 1 變 0 ),可作為一個(gè) 七進(jìn)制計(jì)數(shù)器, Y 輸出進(jìn)位脈沖。

二、狀態(tài)轉(zhuǎn)換圖

三、時(shí)序圖(即: CP 作用下,電路狀態(tài)、輸出狀態(tài)隨時(shí)間變化的波形圖)

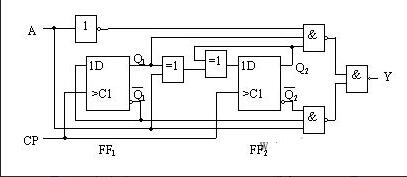

P231 例

解: ( 1 ) 寫出 驅(qū)動(dòng)方程: ![]()

![]()

( 2 ) 由 D 觸發(fā)器特性方程: ![]() 得 狀態(tài)方程:

得 狀態(tài)方程:

![]()

![]()

![]()

![]()

( 3 )輸出方程: ![]()

( 4 )狀態(tài)轉(zhuǎn)換表:

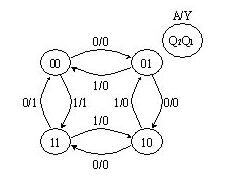

( 5 )狀態(tài)轉(zhuǎn)換圖:

( 6 )邏輯功能: A=0 ,為 4 進(jìn)制加法計(jì)數(shù)器, ![]()

![]() 由 00 、 01 、 10 、 11 遞增,從 11 跳變回 00 時(shí),輸出端 Y 輸出一個(gè)脈沖。A=1 ,為 4 進(jìn)制減法計(jì)數(shù)器,

由 00 、 01 、 10 、 11 遞增,從 11 跳變回 00 時(shí),輸出端 Y 輸出一個(gè)脈沖。A=1 ,為 4 進(jìn)制減法計(jì)數(shù)器, ![]()

![]() 由 11 、 10 、 01 、 00 遞減,從 00 跳變回 11 時(shí),輸出端 Y 輸出一個(gè)脈沖。

由 11 、 10 、 01 、 00 遞減,從 00 跳變回 11 時(shí),輸出端 Y 輸出一個(gè)脈沖。

時(shí)序邏輯電路有哪些(三款時(shí)序邏輯電路的設(shè)計(jì))

時(shí)序邏輯電路的設(shè)計(jì)(一)

下圖的時(shí)序邏輯電路是:設(shè)計(jì)一個(gè)串行數(shù)據(jù)檢測器,對它的要求是:連續(xù)輸入3個(gè)或3個(gè)以上的1時(shí)輸出為1,其他輸入情況下輸出為0。

時(shí)序邏輯電路的設(shè)計(jì)(二)

下圖的時(shí)序邏輯電路是:試用JK觸發(fā)器和門電路設(shè)計(jì)一個(gè)同步七進(jìn)制計(jì)數(shù)器

時(shí)序邏輯電路的設(shè)計(jì)(三)

下圖的時(shí)序邏輯電路是:設(shè)計(jì)一“011”序列檢測器,每當(dāng)輸入011碼時(shí),對應(yīng)最后一個(gè)1,電路輸出為1

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底