一、集成門電路

數字集成電路按其內部有源器件的不同可以分為兩大類:一類為雙極型晶體管集成電路(TTL電路);另一類為單極型集成電路(MOS管組成的電路)。

1.TTL集成邏輯門電路

(1)TTL與非門

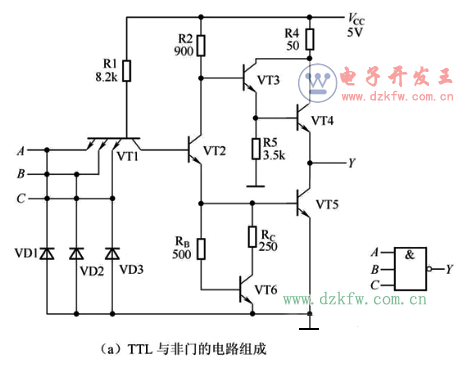

CT74S肖特基系列TTL與非門的電路組成如圖2-19(a)所示,它由輸入級、中間級、輸出級3個部分組成。

圖2-19 TTL與非門電路圖

輸入級:由多發射極管VT1和電阻R1組成,多發射極管的3個發射結為3個PN結。其作用是對輸入變量A、B、C實現邏輯與,所以它相當于一個與門。

中間級:由VT2、R2和VT6、RB、RC組成,VT2集電極和發射極同時輸出兩個邏輯電平相反的信號,用以驅動VT3和VT5。

輸出級:由VT3、VT4、VT5和R4、R5組成,它采用了達林頓結構,VT3和VT4組成復合管降低了輸出高電平時的輸出電阻,提高了帶負載能力。

TTL 與非門的邏輯符號如圖 2-19(b)所示;邏輯表達式為:

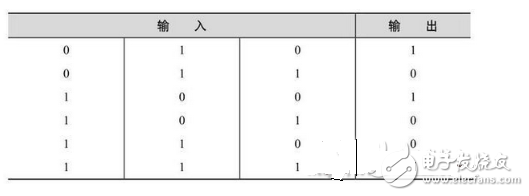

對圖2-19所示電路,如果高電平用1表示,低電平用0表示,則可列出圖2-19所示的真值表,如表2-1所示。

表2-1 TTL與非門真值表

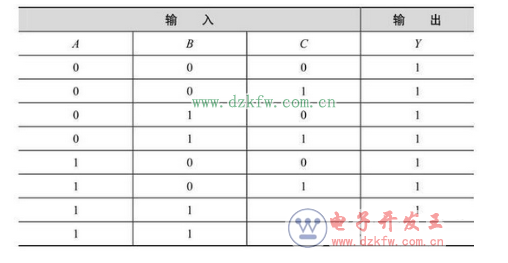

(2)集電極開路與非門(OC門)

① 工作原理。

集電極開路與非門也叫 OC 門,能使門電路輸出的電壓高于電路的高電平電壓值,且門電路的輸出端可以并聯以實現邏輯與功能,即線與(一般的TTL門電路不能線與)。

OC門的電路如圖2-20(a)所示,邏輯符號如圖2-20(b)所示,邏輯表達式為:

圖2-20 集電極開路與非門及邏輯符號

② OC 門的應用。

OC門可以實現線與,如圖2-21所示,邏輯表達式為![]() ;驅動顯示器、實現電平轉換,如圖2-22所示。

;驅動顯示器、實現電平轉換,如圖2-22所示。

圖2-21 用OC門實現線與

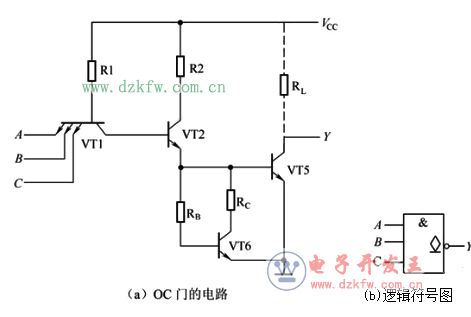

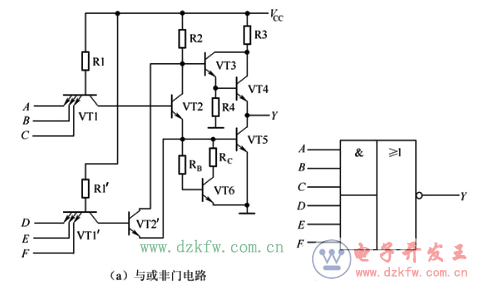

(3)與或非門

與或非門電路如圖2-23(a)所示,邏輯符號如圖2-23(b)所示,邏輯表達式為:

圖2-22 驅動顯示器、實現電平轉換

圖2-23 與或非門及邏輯符號

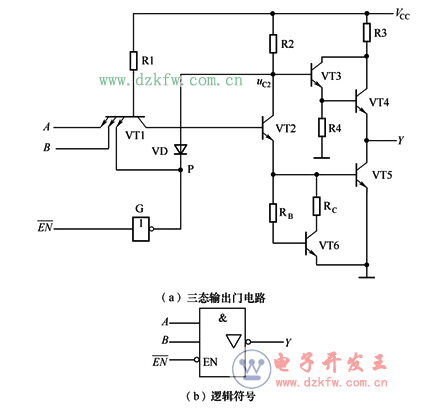

(4)三態輸出門

三態輸出門是指不僅可輸出高電平、低電平兩個狀態,而且還可輸出高阻狀態的門電路,如圖2-24所示,![]() 為控制端。

為控制端。

當![]() =0時,G輸出P=1,VD截止,輸出Y=

=0時,G輸出P=1,VD截止,輸出Y=![]() ,三態門處于工作狀態。

,三態門處于工作狀態。![]() 低電平有效。

低電平有效。

圖2-24 三態輸出與非門及其邏輯符號

當![]() =1時,G輸出P=0,VD導通,輸出高阻狀態。

=1時,G輸出P=0,VD導通,輸出高阻狀態。

2.CMOS集成邏輯門

和 TTL 數字集成電路相比,CMOS 電路的突出特點是微功耗、高抗干擾能力。

(1)CMOS反相器

由兩個場效應管組成互補工作狀態,如圖 2-25 所示。邏輯表達式為:

圖2-25 CMOS 反相器

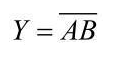

(2)CMOS與非門

如圖2-26所示,兩個串聯的增強型NMOS管VTN1和VTN2為驅動管,兩個并聯的增強型PMOS管VTP1和VTP2為負載管,組成CMOS與非門,邏輯表達式為: 。

。

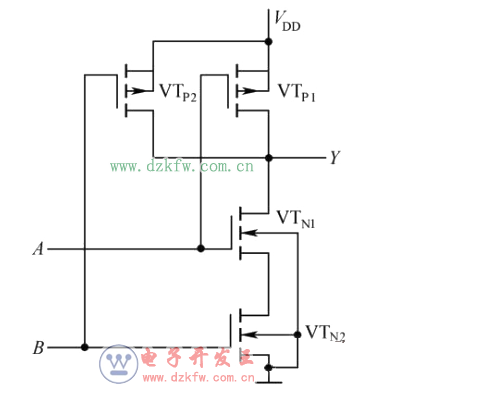

(3)CMOS或非門

如圖2-27所示,兩個并聯的增強型NMOS管VTN1和VTN2為驅動管,兩個串聯的增強型PMOS管VTP1和VTP2為負載管,組成CMOS或非門,邏輯表達式為:

圖2-26 CMOS 與非門

圖2-27 CMOS 或非門

(4)CMOS傳輸門

將兩個參數對稱一致的增強型NMOS管VTN和PMOS管VTP并聯可構成CMOS傳輸門,電路和邏輯符號如圖2-28所示。

圖2-28 CMOS 傳輸門及邏輯符號

(5)CMOS三態門

圖 2-29(a)所示為低電平控制的三態門輸出,圖 2-29(b)為邏輯符號。

圖2-29 CMOS 三態門輸出及邏輯符號

當![]() 時,VTP2和VTN2導通,VTN1和VTP1組成的CMOS反相器工作,所以

時,VTP2和VTN2導通,VTN1和VTP1組成的CMOS反相器工作,所以 。

。

當![]() ,VTP2和VTN2同時截止,輸出Y對地和對電源VDD都呈高阻狀態。

,VTP2和VTN2同時截止,輸出Y對地和對電源VDD都呈高阻狀態。

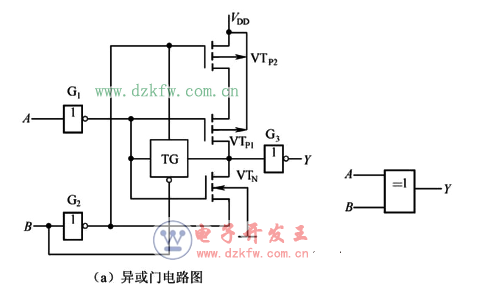

(6)CMOS異或門

圖2-30(a)所示為異或門,圖2-30(b)為邏輯符號。

圖2-30 CMOS 異或門及邏輯符號

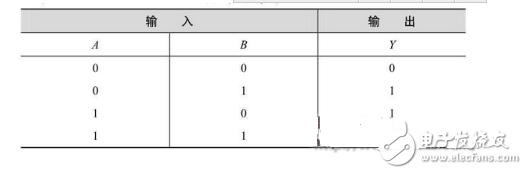

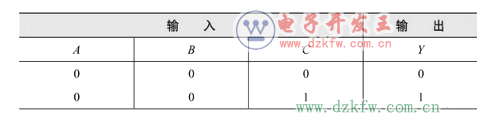

當輸入A=B=0或A=B=1時,即輸入信號相同,輸出Y=0;當輸入A=1或B=1時,即輸入信號不同,輸出Y=1。其真值表如表2-2所示。

表2-2 異或門真值表

3.復合門電路

除了上述介紹的邏輯門電路外,還有或非門、異或門、同或門等,表2-3是基本門和常用復合門的邏輯符號、邏輯表達式及邏輯功能。

表2-3 基本門和常用復合門的對照表

二、組合邏輯電路

邏輯電路在任何時刻的輸出狀態只取決于這一時刻的輸入狀態,而與電路的原來狀態無關,則該電路稱為組合邏輯電路。

1.組合邏輯電路的分析方法

(1)分析步驟

① 根據給定的邏輯電路寫出輸出邏輯關系式。一般從輸入端向輸出端逐級寫出各個門輸出對其輸入的邏輯表達式,從而寫出整個邏輯電路的輸出對輸入變量的邏輯函數式。必要時,可進行化簡,求出輸出邏輯函數式。

② 列出邏輯函數的真值表。將輸入變量的狀態以自然二進制數順序的各種取值組合代入輸出邏輯函數式,求出相應的輸出狀態,并填入表中,即得真值表。

③ 根據真值表和邏輯表達式對邏輯電路進行分析,最后確定其功能。

(2)分析舉例

分析圖2-31所示邏輯電路的功能。

圖2-31 邏輯電路

① 寫出輸出邏輯函數表達式:

② 列出邏輯函數的真值表。將輸入A、B、C取值的各種組合代入式(2-5)中,求出輸出Y的值。由此列出真值表,見表2-4。

表2-4 真值表

續表

③ 邏輯功能分析。由表2-4可知:在輸入A、B、C這3個變量中,有奇數個1時,輸出Y為1,否則Y為0,由此可知,圖2-34為這3位奇校驗電路。

2.組合邏輯電路的設計方法

(1)設計步驟

組合邏輯電路的設計,應以電路簡單、所用器件最少為目標,其設計步驟為:

① 分析設計要求,列出真值表;

② 根據真值表寫出輸出邏輯函數表達式;

③ 對輸出邏輯函數進行化簡;

④ 根據最簡輸出邏輯函數式畫邏輯圖。

(2)設計舉例

設計一個A、B、C3個人表決電路。當表決某個提案時,多數人同意,提案通過,同時A具有否決權。用與非門實現。

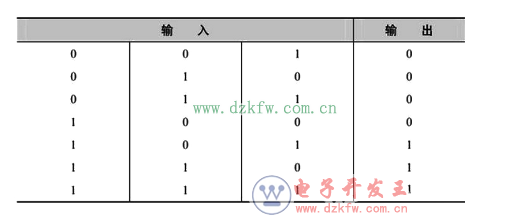

① 分析設計要求,列出真值表,見表2-5。設A、B、C同意提案用1表示,不同意用0表示,Y為表決結果,提案通過為1,通不過為0。

表2-5 真值表

續表

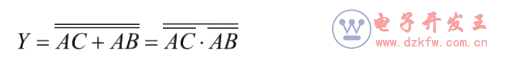

② 將輸出邏輯函數化簡,變換為與非表達式。由圖 2-32 的卡諾圖進行化簡,可得

圖2-32 卡諾圖

將上式變化為與非表達式

③ 根據輸出邏輯函數式(2-6)畫邏輯圖,如圖2-33所示。

3.組合邏輯電路中的競爭冒險

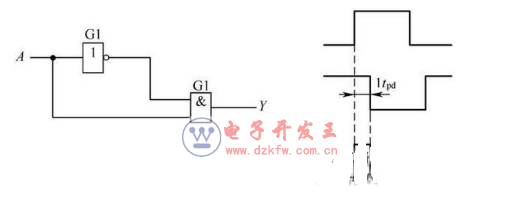

(1)競爭冒險現象及其產生的原因

信號通過導線和門電路時,都存在時間的延遲,信號發生變化時也有一定的上升時間和下降時間。因此,同一個門的一組輸入信號,通過不同數目的門,經過不同長度導線的傳輸,到達門輸入端的時間會有先有后,這種現象稱為競爭。

圖2-33 邏輯電路

邏輯門因輸入端的競爭而導致輸出產生不應有的尖峰干擾脈沖(又稱過渡干擾脈沖)的現象,稱為冒險。如圖2-34所示。

圖2-34 產生正尖峰干擾脈沖冒險

(2)冒險現象的判別

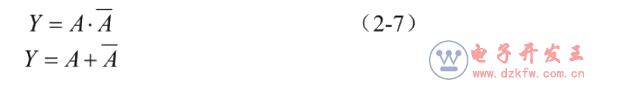

在組合邏輯電路中,是否存在冒險現象,可通過邏輯函數來判別。如果根據組合邏輯電路寫出的輸出邏輯函數在一定條件下可簡化成下列兩種形式時,則該組合邏輯電路存在冒險現象,即:

例如,函數式 ,在A=C=0時,

,在A=C=0時, 。若直接根據這個邏輯表達式組成邏輯電路,則可能出現競爭冒險。

。若直接根據這個邏輯表達式組成邏輯電路,則可能出現競爭冒險。

(3)消除冒險現象的方法

①增加多余項。例如: ,當A=1,C=1時,存在著競爭冒險。根據邏輯代數的基本公式,增加一項 AC,函數式不變,卻消除了競爭冒險,即

,當A=1,C=1時,存在著競爭冒險。根據邏輯代數的基本公式,增加一項 AC,函數式不變,卻消除了競爭冒險,即 。

。

② 加封鎖脈沖。在輸入信號產生競爭冒險時間內,引入一個脈沖將可能產生尖峰干擾脈沖的門封鎖住。封鎖脈沖應在輸入信號轉換前到來,轉換后消失。

③ 加選通脈沖。對輸入可能產生尖峰干擾脈沖的門電路增加一個接選通信號的輸入端,只有在輸入信號轉換完成并穩定后,才引入選通脈沖將它打開,此時才允許有輸出。

④ 接入濾波電容。如果邏輯電路在較慢速度下工作,可以在輸出端并聯一電容器。由于尖峰干擾脈沖的寬度一般都很窄,因此用電容即可吸收掉尖峰干擾脈沖。

⑤ 修改邏輯設計。

三、時序邏輯電路

與組合邏輯電路不同,時序邏輯電路在任何一個時刻的輸出狀態不僅取決于當時的輸入信號,而且還取決于電路原來的狀態。

1.同步時序邏輯電路的分析方法

(1)分析步驟

① 寫方程式。寫出時序邏輯電路的輸出邏輯表達式(即輸出方程)、各觸發器輸入端的邏輯表達式(即驅動方程)和時序邏輯電路的狀態方程。

② 列狀態轉換真值表。將電路現狀的各種取值代入狀態方程和輸出方程中進行計算,求出相應的次態和輸出,從而列出狀態轉換真值表。

③ 邏輯功能的說明。根據狀態轉換真值表來說明電路的邏輯功能。

④ 畫出狀態圖和時序圖。

(2)分析舉例

分析圖 2-35 所示電路的邏輯功能,并畫出狀態轉換圖和時序圖。

圖2-35 待分析邏輯電路圖

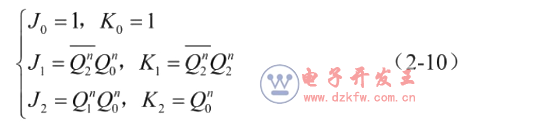

① 寫方程式:

輸出方程:![]()

驅動方程:

狀態方程:將驅動方程式代入 JK 觸發器的特性方程Qn+1=![]() ,得到電路的狀態方程為

,得到電路的狀態方程為

②列狀態轉換真值表:該電路的現狀為![]() ,代入輸出方程(2-9)和狀態方程(2-11)中進行計算后得 Y=0 和

,代入輸出方程(2-9)和狀態方程(2-11)中進行計算后得 Y=0 和![]() ,然后再將001當作現態代入狀態方程式(2-11),得

,然后再將001當作現態代入狀態方程式(2-11),得![]() ,以此類推。可求得可求得表2-6所示的狀態轉換真值表。

,以此類推。可求得可求得表2-6所示的狀態轉換真值表。

表2-6 狀態轉換真值表

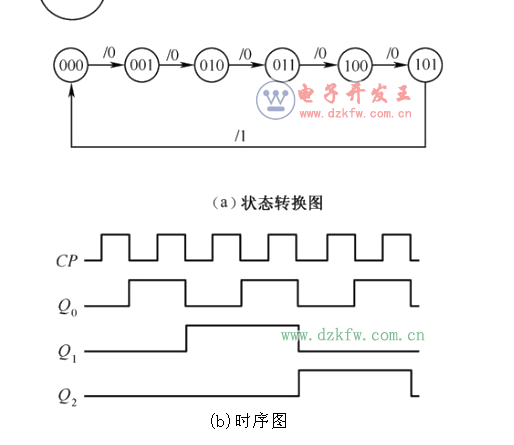

③ 邏輯功能說明:由表2-6可看出,圖2-35所示電路在輸入第六個計數脈沖CP,返回原來的狀態,同時輸出端Y輸出一個進位脈沖。因此,該電路為同步六進制計數器。

圖2-36 狀態轉換圖和時序圖

④ 畫狀態轉換圖和時序圖。根據表2-6可畫出圖2-36(a)所示的狀態轉換圖。圖中的圓圈內表示電路一個狀態,箭頭表示狀態轉換方向,箭頭線上方標注X/Y為轉換條件,X為轉換前輸入變量的取值, Y為輸出值,由于本例沒有輸入變量,故X未標上數值。

2.同步時序邏輯電路的設計方法

同步時序邏輯電路的設計和分析正好相反,根據給定邏輯功能的要求,設計同步時序邏輯電路。設計的關鍵是根據設計要求確定狀態轉換的規律和求出各觸發器的驅動方程。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底