差分動(dòng)放大器原理

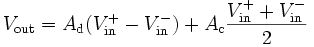

差分放大器也叫差動(dòng)放大器是一種將兩個(gè)輸入端電壓的差以一固定增益放大的電子放大器,有時(shí)簡(jiǎn)稱為“差放”。差分放大器通常被用作功率放大器(簡(jiǎn)稱“功放”)和發(fā)射極耦合邏輯電路 (ECL, Emitter Coupled Logic) 的輸入級(jí)。如果Q1 Q2的特性很相似,則Va,Vb將同樣變化。例如,Va變化+1V,Vb也變化+1V,因?yàn)檩敵鲭妷篤OUT=Va-Vb=0V,即Va的變化與Vb的變化相互抵消。這就是差動(dòng)放大器可以作直流信號(hào)放大的原因。 若差放的兩個(gè)輸入為 ,則它的輸出Vout為:

,則它的輸出Vout為:

其中Ad是差模增益 (differential-mode gain),Ac什模增益 (common-mode gain)。

因此為了提高信/噪比,應(yīng)提高差動(dòng)放大倍數(shù),降低共模放大倍數(shù)。二者之比稱做共模仰制比(CMRR, common-mode rejection ratio)。共模放大倍數(shù)AC可用下式求出:

Ac=2Rl/2Re

通常以差模增益和共模增益的比值共模抑制比 (CMRR, common-mode rejection ratio) 衡量差分放大器消除共模信號(hào)的能力:

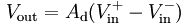

由上式可知,當(dāng)共模增益Ac→0時(shí),CMRR→∞。Re越大,Ac就越低,因此共模抑制比也就越大。因此對(duì)于完全對(duì)稱的差分放大器來說,其Ac = 0,故輸出電壓可以表示為:

所謂共模放大倍數(shù),就是Va,Vb輸入相同信號(hào)時(shí)的放大倍數(shù)。如果共模放大倍數(shù)為0,則輸入噪聲對(duì)輸出沒有影響。

要減小共模放大倍數(shù),加大RE就行通常使用內(nèi)阻大的恒流電路來帶替RE

差分放大器是普通的單端輸入放大器的一種推廣,只要將差放的一個(gè)輸入端接地,即可得到單端輸入的放大器。很多系統(tǒng)在差分放大器的一個(gè)輸入端輸入反饋信號(hào),另一個(gè)輸入端輸入反饋信號(hào),從而實(shí)現(xiàn)負(fù)反饋。常用于電機(jī)或者伺服電機(jī)控制,穩(wěn)壓電源,測(cè)量?jī)x器以及信號(hào)放大。在離散電子學(xué)中,實(shí)現(xiàn)差分放大器的一個(gè)常用手段是差動(dòng)放大,見于多數(shù)運(yùn)算放大器集成電路中的差分電路。

單端輸出的差動(dòng)放大電路 (不平衡輸出)

稱為單端Single ended或不平衡輸出Unbalance Output。

單端較差動(dòng)輸出之幅度小一倍,使用單端輸出時(shí),共模訊號(hào)不能被抑制,因Vi1與Vi2同時(shí)增加,VC1與VC2則減少,而且VC1=VC2,但Vo =VC2,并非于零(產(chǎn)生零點(diǎn)漂移)。

但是加大RE阻值可以增大負(fù)回輸而抑制輸出,并且抑制共模訊號(hào),因Vi1=Vi2時(shí),

Ii1及Ii2也同時(shí)增加,IE亦上升而令VE升高,這對(duì)Q1和Q2產(chǎn)生負(fù)回輸,

令Q1和Q2之增益減少,即Vo減少。

當(dāng)差動(dòng)訊號(hào)輸入時(shí),Vi1 = -Vi2,IC1增加而IC2減少,總電流IE = IC1 + IC2便不變,

因此VE也不變,加大RE電阻值之電路會(huì)將差動(dòng)訊號(hào)放大,不會(huì)對(duì)Q1及Q2產(chǎn)生負(fù)回輸

及抑制。 使用恒流源的差動(dòng)放大器

實(shí)際上,RE不能加得太大,因會(huì)使靜態(tài)之IC1和IC2減少,使Q1和Q2得不到適當(dāng)

實(shí)際上,RE不能加得太大,因會(huì)使靜態(tài)之IC1和IC2減少,使Q1和Q2得不到適當(dāng) 之偏壓或需要很高之電源電壓。 上圖Q3及Q4為電流鏡像恒流源代替電阻RE,使用恒流源可以得到高阻抗及固定電流,

B極因R1和R2得到一個(gè)固定的偏壓。 共模輸入時(shí),Vi1=Vi2,因IE為不變,IC1和IC2也不能改變,故Vo為零,而共模信號(hào)被抑制。 差動(dòng)輸入時(shí),Vi1=-Vi2,雖然IE為不變,但I(xiàn)C1和IC2也可改變,因IC1上升而IC2下降,

故此Vo不等于零,而將差動(dòng)信號(hào)放大。 使用電流鏡像作為差動(dòng)放大器之有源負(fù)載:

主動(dòng)式負(fù)載Active Load (有源負(fù)載)作用:

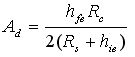

主動(dòng)式負(fù)載Active Load (有源負(fù)載)作用: a)提高增益:

。

。 b)減低功率消耗(相對(duì)純電阻來說)。

c)提高差動(dòng)放大之輸出電壓。

d)提高共模抑制比CMRR。

工作原理:

設(shè)Vi1增加,則Vi2減少(但數(shù)量相等,Vi1 = Vi2)

即差動(dòng)輸入,則IC1升而IC2下降(并且,ΔIC1 = ΔIC2)

因電流鏡像原理,IC4 = IC1

故此,Io = IC4 IC2 = IC1 IC2 (ΔIo = 2ΔIC1或2ΔIC2)

這說明了輸出電流是IC1和IC2的相差,即將輸出變?yōu)榫哂须p端差動(dòng)輸出性能的單端輸出

(故對(duì)共模訊號(hào)之抑制有改善因雙端差動(dòng)輸出才能產(chǎn)生消除共模訊號(hào)作用)。

IC2減少使Q2之VCE增加,使Vo上升而IC4增加,使Q4之VCE減少,這也是使Vo增加,

故此,Vo上升之幅度是使用電阻為負(fù)載之單端輸出電壓大一倍。

返回頂部

返回頂部 刷新頁(yè)面

刷新頁(yè)面 下到頁(yè)底

下到頁(yè)底