PART– 0 基礎知識

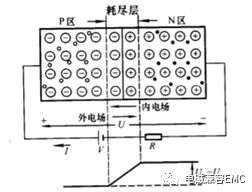

在講MOS管之前,我們來回憶一下半導體材料。如下圖:

做筆記:

N型半導體雜質為P原子,多子為電子

P型半導體雜質為B原子,多子為空穴

由于雜質半導體中有可自由移動的多子,當N型半導體跟P型半導體相接觸,多子發生擴散運動,自由電子與自由空穴復合形成空間電荷區,也就是我們常說的耗盡層。

再做個筆記:耗盡層中沒有自由移動的導電粒子。

PN結的結電容的充電過程,實際上可以近似地看做對耗盡層復合的自由帶電粒子進行補充。

外加電壓:

當PN結外接正偏電壓高于PN結兩端勢壘區的電壓時,耗盡層導電粒子補充完畢,可以跟正常雜質半導體一樣具備導電能力,電路導通。

相反的,如果PN結外接反偏電壓,耗盡層擴大,電路截止。

PART-1 MOS管結構

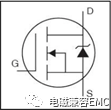

下文開始介紹MOS管,以增強型N-MOSFET為例子進行講解。

增強型N-MOSFET,全稱:N溝道增強型絕緣柵場效應管,在講解其結構前,請讀者記住幾個關鍵詞:

① N溝道

② 絕緣柵

③ 增強型

④ 體二極管

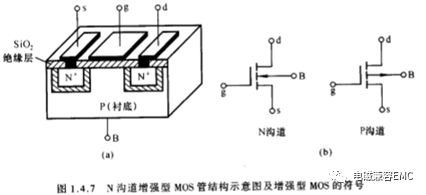

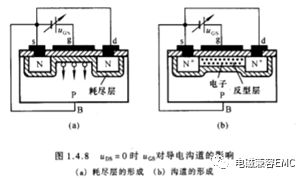

如模電書(童詩白,第四版)中我們熟悉的結構示意圖所示,N溝道增強型MOSFET的結構可視為:

在P型半導體襯底上,制作兩個N型半導體區域并引兩個金屬電極,作為源極S與漏極D;并在P襯底上制作一層SiO2絕緣層,另外引一個金屬電極作為柵極G。

其結構特征可解釋為以下幾點:

①由于N型半導體直接加在P型半導體襯底上,兩個N區與P區之間會形成耗盡層。

②由于柵極G是加在SiO2絕緣層上,與P型半導體襯底間并不導電,只有電場作用

③柵極G外加電場后,吸引P型半導體中的自由電子,同時填充耗盡層,形成反型層導電溝道,連接兩個N型半導體區域,使得增強型N-MOSFET導通。

④ 工藝上制作N-MOSFET時,將源極S與P型半導體襯底直接連接,源極S等同于P型半導體襯底,與漏極D的N型半導體區之間有一個PN結,該PN結即為N-MOSFET的體二極管。

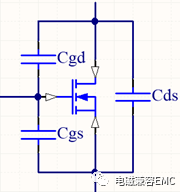

⑤如上圖所示,增強型N-MOSFET各電極之間各有一個寄生電容,其中源極S與漏極D之間的電容Cds為其輸出電容,結構上為體二極管位置PN結的結電容;柵極G與S極、D極之間的寄生電容Cgd、Cgs之和為輸入電容,實質上為形成反型層而吸引的電子(至于為何分為兩個電容,下文講解MOS管開關過程的時候繼續解釋)。

PART-2 MOS管導通過程

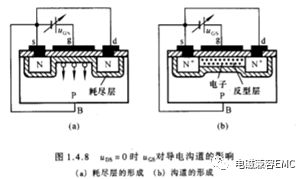

MOS管的導通過程,其實就是形成反型層導電溝道的過程。

重新看回這張圖,當柵極G與源極S之間加一個正偏電壓Vgs時,增強型N-MOSFET的P型半導體襯底中的電子受電場作用,會被吸引到柵極附近,同時連接兩個N型半導體區域,形成反型層導電溝道。

!敲黑板!劃重點!

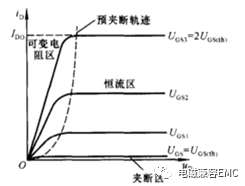

導電溝道剛剛形成的時候那個正偏電壓Vgs,稱為開啟電壓Vgs(th)(或稱為“閾值電壓”);Vgs大于Vgs(th)的這一段電壓區間,稱為可變電阻區,MOS管漏極D到源極S的導通阻抗隨Vgs增大而降低;當Vgs大于2×Vgs(th)之后,基本視為導通阻抗Rds-on降為最低,s且在溫度一致時保持不變,此時增強型N-MOSFET視為完全導通。如下圖

故設置開關MOS管驅動電壓時,一般設置為遠大于2×Vgs(th)。

模電書中給了這么一組圖,闡述了當Vgs大于開啟電壓時,Vds的增大對于流過MOS管的電流iD的影響。

實際上將圖序反過來,可以近似地模擬MOS管開啟過程反型層的行程過程:

MOS管導電過程可近似理解為:

①由于電場作用,先形成靠近源極S區域的反型層,使得MOS管漏極D到源極S之間可以導通并流過電流iD。

②iD開始流過的同時,反型層逐漸向漏極D擴大,并最終使得靠近漏極D的反型層與靠近源極S的反型層寬度基本一致。

③反型層繼續擴大,Rds-on一直降至完全導通,保持不變。

給Cgd充電的過程,Vgs保持不變,此時Rds-on較大,當流過電流iD一定時,MOS管損耗較大。

當柵極G外接電壓,MOS管導通過程,Vgs保持不變的區間稱為米勒區間,由于反型層的形成過程而影響的Vgs、Rds-on及MOS管損耗變化過程的現象稱為米勒效應。下面結合波形詳細介紹一下米勒效應。

這是在論壇中一個博客截的一個圖,已經很形象地體現了外加柵極驅動性號時,MOS管相關電流電壓的變化情況。

(見底部原文鏈接)

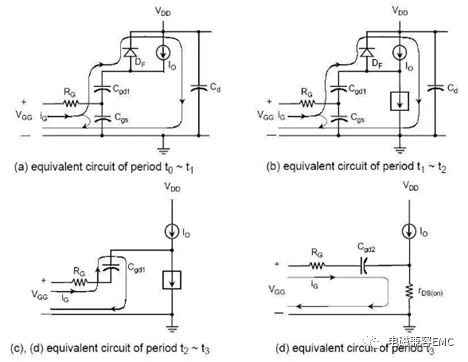

t0-t1:由于柵極電壓未到達開啟電壓,MOS管未導通,如下圖

t1-t2: Vgs到達了開啟電壓,MOS管開始導通,反型層不斷拓寬,柵極電壓繼續升高,如下圖:

t2-t3: MOS管位于可變電阻區,保持持續導通,反型層往漏極側拓寬(大致如下圖紅框中區域),柵極電壓不變,進入米勒平臺:

t3-t4:反型層基本拓寬到寬度一致的情況,柵極繼續施加驅動電壓,整個反型層一齊拓寬,直至柵極電壓Vgs與驅動信號源一致,導通阻抗Rds-on:

用MOS管模型看的話,大致如下側四圖,也就解釋了為什么反型層的輸入電容Ciss要被劃分為兩個電容Cgs跟Cgd,是因為二者的充電順序不一樣:

PART-3MOS管參數

相信各位讀者對MOS管的參數已經耳熟能詳了,這里就不再詳細說明了,參照上文博客中給出的介紹,這里僅對其中部分參數進行補充說明:

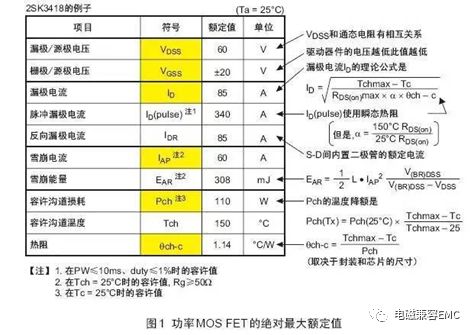

1)、功率MOSFET的絕對最大額定值:

注①:漏源最大電壓VDSS,可視為反向施加在體二極管兩端的電壓值,故只有一個方向。

注②:柵源最大電壓VGSS,即施加在柵極電極與源極電極之間的電壓,由于柵極與P型半導體襯底中加了SiO2絕緣層,只要電壓絕對值超過絕緣層耐壓均會擊穿,故有兩個方向“±”。

注③:漏級最大電流ID與體二極管流過的反向漏級最大電流IDR(或稱為IS)一般規格書中數值一致,均為流過N型半導體與P型半導體襯底形成的PN結的最大電流。

注④:ID(pulse)需要看施加電流的脈沖寬度,脈寬不一致的不能沿用規格書數據。

注⑤:雪崩電流IAP同樣需要關注脈沖寬度。

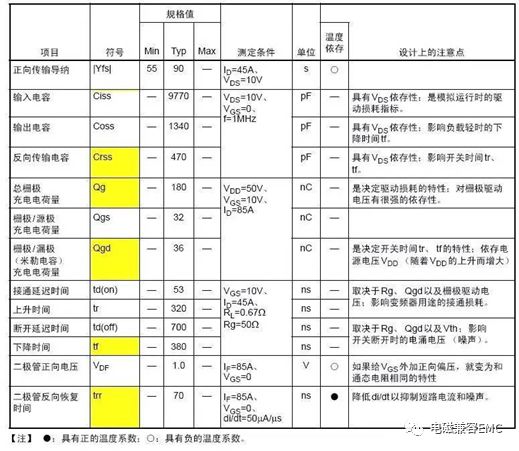

2)、靜態電特性

注①:Vgs(off)其實就是開啟電壓Vgs(th),只不過這里看的角度不一樣。

注②:看完前文的讀者應該知道為什么這里兩個Rds(on)大小有差異,不知道的回去前面重新看。

3)、動態點特性

注①:Ciss = Cgs + Cgd ;Coss = Cds ;Crss = Cgd

注②:MOS管開啟速度最主要關注的參數是Qg,也就是形成反型層需要的總電荷量!

注③:接通/斷開延遲時間t d(on/off)、上升/下降時間tr / tf,各位工程時使用的時候請根據實際漏級電路ID,柵極驅動電壓Vg進行判斷。

MOS的介紹基本如上,時間及篇幅關系文中不涉及具體電路講解。圖源及主要參考書籍為《模擬電子技術基礎,(童詩白.第4版)》,《電子技術基礎.模擬部分.(康華光.第5版)》,各位工程師工作時多看會大學課本有時會有不同的收獲。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底